# 결함접지구조(Defected Ground Structure)를 갖는 휴대 인터넷용 소형 고전력 SPDT PIN 다이오드 스위치 설계

Design of Small-Size High-Power SPDT PIN Diode Switch with Defected Ground Structure for Wireless Broadband Internet Application

김 동 욱

Dong-Wook Kim

요 약

본 논문에서는 결함접지구조(Defected Ground Structure: DGS)의 전파 지연 특성을 이용하여 소형으로 구현한 휴대 인터넷용 고전력 Single Pole Double Throw(SPDT) 스위치의 특성이 제공되며 1/4 파장 전송선을 이용하여 제작된 일반적인 방식의 스위치와 그 특성이 비교된다. DGS를 활용하여 제작된 스위치는 높은 격리도를 확보하기 위해 병렬구조의 다이오드를 사용하여 구성되었으며 2.3 GHz에서 0.8 dB의 삽입 손실과 50 dB 이상의 격리도 특성을 보였고 50 W 이상의 전력을 다룰 수 있었다. DGS를 활용한 스위치는 기존의 전송선 방식의 스위치와 거의 동일한 스위칭 특성을 보이면서도 50 % 가까운 회로의 크기 감소를 달성할 수 있었다.

#### Abstract

In this paper, small-size high-power single pole double throw(SPDT) switch with defected ground structure(DGS) is presented for wireless broadband internet application. To reduce the circuit size using slow-wave characteristic, the DGS is applied to  $\lambda/4$  transmission line of the switch and the measured results are compared with them of conventional switch. To secure high degree of isolation, the switch with the DGS is composed of shunt-connected PIN diodes and shows insertion loss of 0.8 dB and isolation more than 50 dB at 2.3 GHz. The size of the switch is reduced about 50 % only with the DGS patterns while it has very similar performance to the conventional shunt-type switch.

Key words: Defected Ground Structure, PIN Diode, SPDT, Wireless Broadband Internet

#### I. 서 론

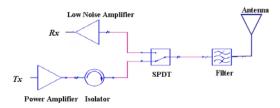

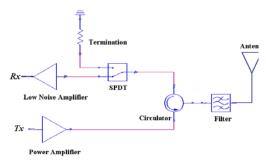

휴대폰을 이용한 인터넷 사용이 급증함에 따라 무선 인터넷에 대한 필요성이 증가되었다. 2.3 GHz 주파수 대역을 사용하는 시간분할 통신방식의 와이 브로(Wibro: Wireless Broadband Internet)는 이러한 사 용자의 요구를 충족시켜 줄 수 있는 휴대 인터넷 서 비스이다. 와이브로 서비스를 위한 시스템은 개략적 으로 두 가지로 구성될 수 있는데, 하나는 그림 1(a) 와 같이 스위치를 Tx 경로와 Rx 경로를 절환하는데 사용하는 방식이고 또 다른 하나는 그림 1(b)처럼 스 위치를 Rx 경로에만 두는 방식이다. 후자의 경우 Tx 경로에서 스위치를 제거할 수 있어 Tx 손실을 줄일 수 있고 스위치의 격리도에 대한 요구조건을 다소 완화할 수 있어 시스템 측면에서 다소 유리한 점이 있다.

본 논문에서는 후자의 시스템에 적용하기 위한 single pole double throw(SPDT) 스위치를 설계, 제작

<sup>「</sup>이 논문은 2005년도 충남대학교 학술연구비 지원에 의하여 연구되었음.」

충남대학교 전파공학과(Department of Radio Science and Engineering, Chungnam National University)

<sup>·</sup>논 문 번 호 : 20050816-088 ·수정완료일자 : 2005년 9월 23일

- (a) 스위치를 Tx-Rx 절환에 사용하는 방식

- (a) Switching of Tx path and Rx path

- (b) 스위치를 Rx 경로에 두는 방식

- (b) Switching of LNA and termination resistor on Rx path 그림 1. 와이브로 시스템의 개략적 Tx-Rx 구성도 Fig. 1. Schematic of Tx-Rx block of wibro system.

하고 그 성능을 평가하고자 한다. Tx의 전력증폭기에서 누설된 신호로부터 Rx 회로를 보호하기 위해 40 dB 이상의 충분한 격리도가 확보되어야 하고 시스템의 신호대 잡음 특성의 저하를 막기 위해 스위치의 삽입 손실은 1 dB 이내로 유지되어야 한다. 또한 안테나를 통한 예상치 못한 Tx 신호의 유입에 대비할 수 있도록 스위치의 전력능력은 50 W 이상이되어야 한다. 이러한 특성을 갖는 스위치를 구현하기 위해 병렬(shunt) 구조의 PIN 다이오드를 사용하였고 회로의 크기를 줄이기 위해 1/4 파장 전송선로 대신에 최근 각광을 받고 있는 결함접지구조(Defected Ground Structure: DGS) 회로를 사용하였다.

DGS 회로는 기판의 접지 면에 식각을 통하여 간단한 결함구조를 형성하고 기판의 윗면에는 보통의 전송선로 구조를 가지는 형태로써 제작이 용이하며 특정 대역에서 신호의 저지(rejection) 특성을 보일 뿐만 아니라 신호의 전송속도가 느려지는 특성을 가지고 있다. 이러한 DGS 회로는 필터<sup>[1],[2]</sup>, 증폭기<sup>[3]~[5]</sup>, 주파수 체배기<sup>[6]</sup>, 발진기<sup>[7]</sup> 등의 회로에 응용되었으며 주로 신호의 저지 특성을 활용하였다. 여기서는

회로의 크기를 줄이기 위해 반사가 최소가 되는 DGS 회로의 임피던스를 유지하면서 효과적으로 신호의 속도 지연을 야기하는 패턴을 설계하여 사용하였다. 그리고 이러한 DGS 회로가 적용된 고전력 스위치 회로를 평가하고 일반적인 구조의 스위치 회로와 그 특성을 비교하였다.

### Ⅱ. DGS 회로 설계

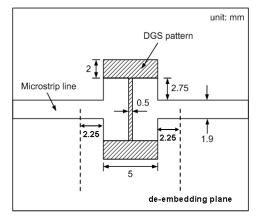

그림 2는 아령 모양의 DGS 회로를 개략적으로 보여주고 있다. 마이크로스트립 전송선로가 기판 위에 형성되어 있고 DGS 패턴은 기판 아래의 접지면에 식각되어져 있다. 그림에 나타난 바와 같이 DGS 패턴은 음영 부분으로 표시되어져 있다. 마이크로스트립 선로 폭은 특성 임피던스가 50 Ω을 가지도록 선택되었고 DGS 패턴에서 식각된 면의 넓이와 간격, 그리고 식각된 패턴 위에 형성된 전송선로의 폭은 3차원 전자파 모의실험을 통해 결정되었다.

DGS 회로를 만들 때 마이크로스트립 전송선로의 접지면을 일부 식각해내는 작업은 전송선로의 직렬 등가 인덕턴스를 증가시키는 역할을 하게 된다. 이러한 인덕턴스의 증가는 신호의 전파 지연 효과를 유발하여 회로의 크기를 줄이는데 기여할 수 있지만 전송선로의 특성 임피던스를 증가시켜 임피던스 부정합에 의한 삽입 손실을 일으킨다. 회로의 손실 특성이 아주 중요한 스위치 회로의 경우 이러한 소자 값의 선택은 적절하지 않으므로 전파 지연 효과를 강

그림 2. 설계된 아령 모양의 DGS 회로 구조도 Fig. 2. Schematic of a dumbbell-shaped DGS pattern.

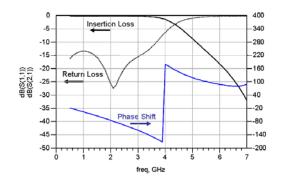

그림 3. 3차원 전자파 모의실험을 통한 DGS 회로의 산란계수 특성

Fig. 3. Simulated scattering parameters of DGS pattern by 3D electromagnetic simulator.

하게 유지하면서 전송선로 임피던스 값을 일반적인 마이크로스트립 전송선로의 특성 임피던스 값에 가깝게 유지하도록 DGS 회로의 전송선로 폭을 넓혀야한다. 이는 전송선로의 단락 커패시턴스를 증가시키는 것과 같기 때문에 전송선로의 임피던스를 낮추어임피던스 부정합을 제거할 수 있게 한다.

다양한 모의실험을 통해 2 mm×5 mm의 식각 영역과 0.5 mm의 식각 면 간격, 7.4 mm의 전송선로 폭이 선택되었고 그림 2에 이를 표시하였다. 사용된기판은 32 mils 두께의 Rogers 기판으로 10 GHz에서유전상수는 3.38, tan6=0.0027을 가진다. 모의실험 결과에 따르면 약 3배의 전파지연 효과가 얻어졌고 5 mm의 DGS 회로에 표면실장 소자 작업을 위한 전송선 공간을 포함하여 9.5 mm의 전송선로를 사용할경우 2.3 GHz에서 90도의 위상 변화를 얻을 수 있었다. 이는 기존의 마이크로스트립 전송선로를 사용할경우 20 mm의 길이가 소요된다는 점을 감안하면 선로의 길이가 크게 줄어들었음을 알 수 있다.

그림 3은 그림 2의 DGS 회로를 3차원 모의실험을 하여 구한 회로의 산란계수와 위상 특성 변화를 보여주고 있다. DGS 회로가 불연속면을 포함하고 있으므로 경계조건으로부터 계산 결과가 영향을 덜 받도록 충분한 크기의 구조에 대해 계산이 수행되었으며 그림 3의 산란계수는 5 mm의 DGS 패턴으로부터 바깥쪽으로 각각 2.25 mm 떨어진 지점까지 de-embedding하여 구한 결과를 보여주고 있다.

Ⅲ. SPDT 스위치 설계

PIN 다이오드는 마이크로웨이브 주파수 대역에서 전류에 의해 제어되는 저항처럼 동작을 하고 작은 양의 DC 전력으로 아주 큰 RF 전력을 제어할 수있기 때문에 고전력 스위치 회로에 많이 사용된다[8],[9]

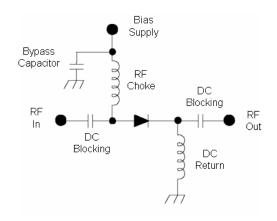

스위치 소자로써 다이오드를 활용하는 가장 간단한 방법으로는 그림 4와 같이 직렬(series) 연결 방식과 병렬(shunt) 연결 방식이 있다. 직렬 연결 방식은 다이오드가 on일 때 낮은 on 저항에 의해 신호가 다이오드를 통해 전송되며 off일 때는 다이오드의 off 커패시턴스에 의한 높은 임피던스로 인해 신호가 차단된다. 병렬 연결 방식은 직렬 연결 방식과 반대로다이오드가 on일 때는 접지로 연결된 다이오드의 낮은 on 저항에 의해 신호가 차단되고 off일 때는 높

- (a) 직렬구조 스위치

- (a) Series-connected switch

- (D) 명일구소 스위시

- (b) Shunt-connected switch

그림 4. 다이오드를 이용한 스위치 회로도 Fig. 4. Diode switch circuits.

은 임피던스를 가지는 다이오드 off 커패시턴스에 의해 신호의 전송이 쉽게 일어난다. 직렬 방식과 병렬 방식의 다이오드 접합에 따른 각 구조의 삽입 손실, 격리도 그리고 소모 전력에 대한 식은 아래와 같이 표현된다<sup>[10]</sup>. 직렬 구조의 경우,

Insertion loss(dB) = 20 log

$$_{10}$$

$\left(1 + \frac{R_S}{2Z_O}\right)$  (1)

$$Isolation(dB) = 10 \log_{10} \left( 1 + \left( \frac{X_C}{2Z_O} \right)^2 \right)$$

(2)

$$P_{D} = \frac{4R_{S}Z_{O}}{(2Z_{O} + R_{S})^{2}} \cdot P_{INC}$$

(3)

이며 병렬 구조의 경우,

Insertion loss(dB) = 10 log

$$_{10} \left( 1 + \left( \frac{Z_o}{2X_c} \right)^2 \right)$$

(4)

$$Isolation(dB) = 20 \log_{10} \left(1 + \frac{Z_0}{2R_S}\right)$$

(5)

$$P_{D} = \frac{4R_{S}Z_{O}}{(Z_{O} + 2R_{S})^{2}} \cdot P_{INC}$$

(6)

이다. 여기서  $R_s$ 는 다이오드의 on 저항,  $X_c$ 는 다이오드의 off 커패시턴스에 의한 리액턴스,  $Z_o$ 는 특성 임피던스, 그리고  $P_{INC}$ 는 입력 RF 전력을 나타낸다. 위식에 나타난 바와 같이 직렬 구조의 격리도는 다이오드의 off 커패시턴스에 의해 좌우되며 삽입 손실과 전력 소모는 순방향 전류조건에서의 다이오드 on 저항에 의해 좌우된다. 병렬 구조의 삽입 손실의 경우 전송선과 직렬로 연결된 스위치 소자가 없으므로 상대적으로 작은 삽입 손실을 구현할 수가 있지만 다이오드의 off 커패시턴스가 클 경우 삽입 손실이 더욱 커질 수 있다.

스위치가 50 W 이상의 RF 전력을 다루기 위해서는 다이오드가 높은 항복전압을 가져야 할 뿐만 아니라 다이오드의 접합(junction) 면적도 커야 한다. 그러나 다이오드의 큰 면적은 off 상태에서 큰 커패 시턴스를 만들어 RF 특성을 급격히 나빠지게 한다. 본 논문의 SPDT 스위치 제작에 사용된 다이오드는 Metelics사에서 제작된 것으로 0.5 Ω의 on 저항과

0.4 pF의 off 커패시턴스, 그리고 200 k ♀ 이상의 병렬 off 저항 특성을 가지고 있다. 식 (2)를 통해서도알 수 있는 바와 같이 이러한 파라미터의 다이오드를 직렬 형태로 스위칭 동작을 시키게 되면 2.3 GHz에서 6 dB 이하의 격리도 특성을 보여 40 dB 이상의격리도를 요구하는 스위치에 적용할 경우 필요 이상의 많은 소자를 사용하게 된다. 또한 병렬 구조의 회로에서 0.5 ♀의 on 저항은 식 (6)이 보여주는 바와같이 1.9 W 이상의 전력 소모를 일으킬 수 있으므로통상 250 mW 정도의 전력 소모만을 견딜 수 있는플라스틱 팩키지 형태의 소자 사용은 피하여야 한다. 따라서 50 W 이상의 전력을 견딜 수 있는 높은격리도의 스위치를 만들기 위해 병렬 구조의 회로를사용하였고 다이오드는 전력 소모를 고려하여 bare die 형태의 칩을 사용하였다.

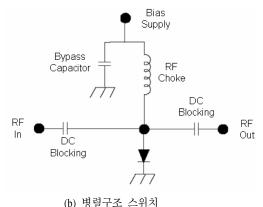

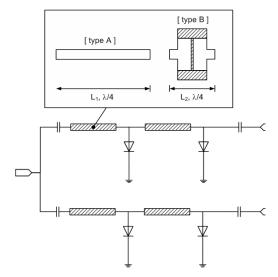

높은 격리도를 유지하면서 고전력을 견디기 위해 구성된 병렬 구조의 스위치 회로가 그림 5에 나타나 있다. 병렬 구조의 회로에서 빗금 친 전송선로 부분은 다이오드에 의한 단락 임피던스를 개방형 임피던스로 바꾸어 주기 위해 사용되었으며 1/4 파장의 길이를 가진다. 빗금 영역의 전송선로를 종래의  $50~\Omega$  전송선로를 사용하여 구성한 스위치 회로(type A)와 DGS 회로를 사용하여 그 크기를 절반 가량 줄인 스위치 회로(type B)로 나누어 설계하고 제작하였다. Type B 회로의 경우  $L_2$ 의 길이는 9.5~mm로 type A 회로의  $L_1$  길이 20~mm보다 훨씬 작다. 5~mm 길이의 DGS 패턴 옆에 연결된 4.5~mm 길이의  $50~\Omega$  전송선로는 표면 실장 부품들의 작업을 위해 편의상 삽입되었으며 실제 DGS 회로의 전송선로 축소 비율은 1/3~정도로 구현되었다.

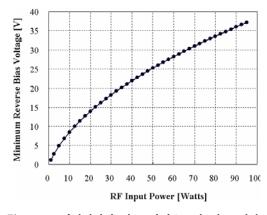

PIN 다이오드로 고전력 스위치를 구현할 때 적정한 역방향 바이어스 전압의 설정은 제한된 전원 조건에서 안정된 동작을 위해 아주 중요하다. RF 전력이 인가된 경우 스위치의 PIN 다이오드에 필요한 최소 역방향 바이어스 전압은 입력 전력에 따라 다르게 나타나며 식 (7)과 같이 계산될 수 있다<sup>111</sup>.

$$|V_{DC}| = \frac{|V_{RF}|}{\left[1 + \left[\pi \cdot f \cdot w^{2}/0.95 \cdot \mu \cdot V_{RF} \cdot \sqrt{D} \left[1 + \sqrt{1 + \left[0.95 \cdot \mu \cdot V_{RF} \cdot \sqrt{D}/W \cdot v_{sat}\right]^{2}\right]\right]^{2}\right]^{0.5}}$$

(7)

그림 5. 병렬구조의 SPDT 다이오드 스위치 회로. Type A: 마이크로스트립 전송선로를 이용한 스위치( $L_1$ =20 mm), Type B: DGS 회로를 이 용한 스위치( $L_2$ =9.5 mm, DGS 폭=5 mm)

Fig. 5. Schematic of SPDT switch with shunt-connected diodes. Type A is with the conventional microstrip lines( $L_1$ =20 mm) and type B is with the DGS patterns( $L_2$ =9.5 mm, DGS width=5 mm).

여기서 f는 신호의 주파수이며 W는 PIN 다이오드의 진성(intrinsic) 영역 두께,  $\mu$ 는 캐리어의 mobility, D는 RF 펄스의 duty cycle을 나타내고  $v_{sat}$ 는 캐리어의 포화속도를 의미한다. RF 펄스의 duty cycle D=1이

그림 6. RF 입력전력에 따른 다이오드의 최소 역방 향 바이어스 전압

Fig. 6. Minimum reverse bias voltage of PIN diode with RF input power level.

고 다이오드의 W=30 µm일 때 식 (7)을 사용하여 입력전력에 따른 최소 역방향 바이어스 전압을 산출하면 그림 6과 같다. 그림에서 알 수 있는 바와 같이 허용되는 전력에 따라 요구되는 전압도 커지게 되는데 50 W RF 전력의 경우 최소 25 V 이상의 역방향전압이 요구된다. 따라서 제작된 스위치 회로는 30 V의 역방향 바이어스 전압을 사용하였다.

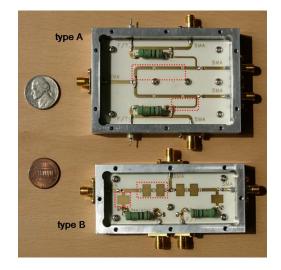

# Ⅳ. 스위치 측정

DGS 회로를 사용하여 크기를 대폭 줄인 스위치 회로와 종래의 1/4 파장 전송선로를 이용한 병렬구조의 스위치 회로를 함께 제작하였고 제작 결과를 그림 7에 나타내었다. DGS 회로에 의한 전송선로의 축소를 보여주기 위해 점선으로 그림에 표시하였고 다이오드의 임피던스 전환과 바이어스 전원 연결을 위한 1/4 파장 전송선로는 대략 50 % 가량 축소되었다.

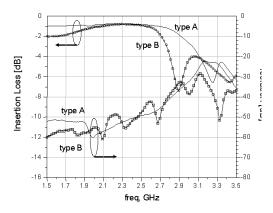

그림 8은 제작된 두 가지 스위치 회로(type A와 type B)에 대한 산란계수 측정 결과를 보여주고 있다. 2.3~2.4 GHz 주파수 영역에서 type A와 type B의 삽입 손실은 각각 0.75 dB와 0.8 dB이며 격리도는 2개의 다이오드만으로도 50 dB 이상의 값을 보여주었다. 두 회로 모두 비슷한 측정값을 보였지만 type B의 경우 PCB의 접지면이 모듈 지그의 금속면과 가

그림 7. 제작된 고전력 SPDT 스위치 모듈

Fig. 7. The fabricated high power SPDT switch module.

그림 8. 측정된 type A와 type B SPDT 스위치 모듈 의 삽입 손실 및 격리도 특성

Fig. 8. The measured insertion loss and isolation of type A and type B SPDT switches.

까이 존재할 때 삽입 손실 및 격리도 특성이 약간 변하였다. 제작된 지그의 경우 4 mm의 금속 두께를 가지고 있었으며 접지면이 PCB 기판으로부터 4 mm까지 접근할 때 0.05~0.1 dB의 삽입 손실 변화를 보였다. 주변 금속 물체에 의한 이러한 특성 변화는 크기가 작다고 해도 작은 삽입 손실 값과 높은 격리도를 요구하는 고전력 회로에 있어서는 고려되어야 할 요소이다. 그러므로 PCB를 지그에 부착할 때 DGS 회로 아래에 충분한 공간이 확보될 수 있도록 설계되어야 할 것이다.

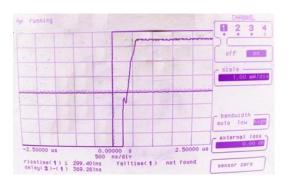

스위치 회로에 대한 전력 측정이 고출력 전력증 폭기를 사용하여 수행되었다. 평균 50 W의 RF 입력 전력에 대해서 두 회로 모두 안정된 동작 특성을 보 였으며, 입력 전력이 60 W를 넘어서면서 본딩 와이 어가 영향을 받기 시작했고, 70 W의 입력전력에 대 해서는 소자가 파괴되는 양상을 보였다. 이는 그림 6에서도 알 수 있는 바와 같이 65 W 이상의 전력이 인가되면 역방향 바이어스 전압이 상대적으로 낮아 RF 신호의 스윙에 대해 다이오드 전류가 급격히 커 져 소자에 치명적 손상을 주기 때문이다. 또한 HP-8990A Peak Power Analyzer를 이용하여 회로의 스위 칭 속도를 측정하였다. 그림 9는 측정된 스위칭 특 성의 한 예를 보여주고 있다. DGS 회로를 사용한 스 위치 회로와 일반적인 전송선로를 사용한 스위치 회 로 모두 320 nsec 이하의 rise time과 fall time을 나타 내어 휴대인터넷 시스템이 요구하는 usec 레벨의

그림 9. DGS 회로를 이용한 고전력 SPDT 스위치의 스위칭 특성

Fig. 9. The switching characteristic of high power SPDT switch with DGS patterns.

스위칭 동작에 만족함을 알 수 있었다.

# V. 결 론

1/4 파장 전송선로에 의한 회로 크기를 줄이기 위 해 DGS 회로를 적용하여 높은 격리도의 2.3 GHz 와 이브로 시스템용 고전력 SPDT 스위치 회로가 설계, 제작되었다. 제작된 회로는 종래의 마이크로스트립 전송선을 사용한 회로와 매우 유사한 0.8 dB의 삽입 손실과 50 dB 이상의 격리도 특성을 보였다. DGS 회 로는 3차원 전자파 모의실험을 통해 설계되었으며 회로의 전파 지연 특성이 최대한 활용되었다. 전력 측정과 스위칭 속도 측정을 통해 제작된 스위치가 50 W 이상의 전력 제어 능력과 usec 이하의 스위칭 속도를 가짐을 알 수 있었다. 그러나 DGS 회로는 특 성상 회로의 2차원 면적을 줄일 수 있었지만 모듈로 제작될 때 모듈의 금속 접지면과의 사이에 일정한 간격이 요구되었다. 따라서 회로 패턴과 모듈 접지 와의 사이에 공간 설계가 적절히 이루어진다면 휴대 인터넷 시스템에 사용되는 소형 고전력 스위치에 DGS 회로가 성공적으로 적용될 수 있음을 보였다.

# 참 고 문 헌

[1] Dal Ahn, Jun-Seok Park, Chul-Soo Kim, Juno Kim, Yongxi Qian, and Tatsuo Itoh, "A design of the low-pass filter using the novel microstrip defected ground structure", *IEEE Trans. Microwave Theory*

- and Tech., vol. 49, no. 1, pp. 86-93, Jan. 2001.

- [2] Hai-Wen Liu, Zheng-Fan Li, Xiao-Wei Sun, and Jun-Fa Mao, "An improved 1-D periodic defected ground structure for microstrip line", *IEEE Microwave and Wireless Components Letters*, vol. 14, no. 4, pp. 180-182, Apr. 2004.

- [3] Jong-Sik Lim, Jun-Seok Park, Yong-Taek Lee, Dal Ahn, and Sangwook Nam, "Application of defected ground structure in reducing the size of amplifiers", *IEEE Microwave and Wireless Components Letters*, vol. 12, no. 7, pp. 261-263, Jul. 2002.

- [4] 이경희, 정용채, "DGS 방식 DC Block을 이용한 증폭기의 설계", 한국전자파학회논문지, 12(3), pp. 432-438, 2001년 4월.

- [5] 정시균, 정용채, "¼4 DGS 바이어스 선로를 이용한 전력증폭기 설계", 한국전자파학회논문지, 13(9), pp. 924-931, 2002년 10월.

- [6] 황도경, 임종식, 정용채, "Feedforward 구조와 DGS를 이용하여 기본 신호와 3차 이상의 고조 파 신호를 제거한 2차 주파수 체배기 설계", 한 국전자파학회논문지, 14(5), pp. 513-520, 2003년 5월.

- [7] Jun-Seok Park, Myeong-Sub Jung, "A novel de-

- fected ground structure for an active device mounting and its application to a microwave oscillator", *IEEE Microwave and Wireless Components Letters*, vol. 14, no. 5, pp. 198-200, May 2004.

- [8] Martin Caulton, Arye Rosen, Paul J. Stabile, and Anna Gombar, "p-i-n diodes for low-frequency high-power switching applications", *IEEE Trans. Microwave Theory and Tech.*, vol. 30, no. 6, pp. 875-882, Jun. 1982.

- [9] Seung-Won Paek, Hyun-Il Kang, Kye-Ik Jeon, Myung-Deuk Jeong, Dong-Wook Kim, Chae-Rok Lim, Jae-Hak Lee, Won-Sang Lee, Jae-Eung Oh, and Ki-Woong Chung, "1~26 GHz high power P-I-N diode switch", IEEE International Microwave Symposium Digest, pp. 505-508, Jun. 2000.

- [10] Gerald Hiller, "Design with PIN diodes", M/A-COM Application Note, AG312, pp. 18-1-18-18.

- [11] Robert H. Caverly, Gerald Hiller, "Establishing the minimum reverse bias for a p-i-n diode in a high-power switch", *IEEE Trans. Microwave Theory and Tech.*, vol. 38, no. 12, pp. 1938-1943, Dec. 1990.

#### 김 동 욱

1990년 2월: 한양대학교 전자통신 공학과 (공학사) 1992년 2월: 한국과학기술원 전기 및 전자공학과 (공학석사) 1996년 8월: 한국과학기술원 전기 및 전자공학과 (공학박사) 1991년 8월~2000년 5월: LG종합

기술원 선임연구원 2000년 6월~2002년 8월: 텔레포스(주) 연구소장 2002년 9월~2004년 9월: 에스원 기술연구소 응용기술팀 장

2004년 10월~현재: 충남대학교 전파공학과 교수 [주 관심분야] 초고속 반도체 소자, 무선통신용 RFIC, 원 격탐지용 초고주파 집적회로