논문 2009-46TC-12-3

## 펄스 타이밍 제어를 활용한 Ka-대역 10 W 전력증폭기 모듈

( A Ka-band 10 W Power Amplifier Module utilizing Pulse Timing Control )

장 석 현\*. 김 경 학\*. 권 태 민\*. 김 동 욱\*\*

(Seok-Hyun Jang, Kyeong-Hak Kim, Tae-Min Kwon, and Dong-Wook Kim)

요 약

본 논문에서는 7개의 MMIC 전력증폭기 칩과 박막기판을 결합하여 MIC 모듈을 구성함으로써 Ka-대역 중심주파수 영역에서 10 W 이상의 출력전력을 가지는 필스모드 전력증폭기 모듈을 설계하고 제작하였다. 전력증폭기 모듈의 제작에는 밀리미터파 대역에 적합한 수정된 형태의 윌킨슨 전력분배기/합성기와 모듈의 조립과정에서 공진을 억제하고 작은 삽입손실 특성을 보이는 CBFGCPW-Microstrip 천이구조를 활용하였다. 전력용 MMIC 바이어스 회로에 사용된 큰 값의 바이패스 캐패시터에 의해 발생되는 필스모드 출력전력의 감소를 개선하고자 TTL 필스 타이밍 제어 기법을 제안하였다. 제안된 방법을 10 kHz, 5 µ sec 필스모드로 동작하는 전력증폭기 모듈에 적용한 결과 필스모드 동작시간을 200 nsec 이상 개선할 수 있었고 0.62 W의 출력전력을 향상시킬 수 있었다. 구현된 전력증폭기 모듈은 59.5 dB의 전력이득과 11.89 W의 출력전력을 보여주었다.

#### **Abstract**

In this paper, a Ka-band 10 W power amplifier module with seven power MMIC bare dies is designed and fabricated using MIC technology which combines multiple MMIC chips on a thin film substrate. Modified Wilkinson power dividers/combiners and CBFGCPW-Microstrip transitions for suppressing resonance and reducing connection loss are utilized for high-gain and high-power millimeter wave modules. A new TTL pulse timing control scheme is proposed to improve output power degradation due to large bypass capacitors in the gate bias circuit. Pulse-mode operation time is extended more than 200 nsec and output power increase of 0.62 W is achieved by applying the proposed scheme to the Ka-band 10 W power amplifier module operating in the pulsed condition of 10 kHz and 5 µsec. The implemented power amplifier module shows a power gain of 59.5 dB and an output power of 11.89 W.

Keywords: Power amplifier module, Ka-band, pulse timing control

#### I. 서 론

전력증폭기는 휴대단말기, 이동통신 기지국 장비, 레이더 등에서 RF 신호를 증폭하여 출력단에 전달하는 기능을 하는 핵심부품이다. 초기의 전력증폭기는 하이 브리드(hybrid)의 형태로 제작되었으나, 80년대 이후 화합물 반도체 공정기술의 발전과 설계 소프트웨어 및 소

자 모델링 기술의 비약적인 발전으로 인해 MMIC (Monolithic Microwave Integrated Circuit)의 형태로 주로 제작되어지고 있는 추세이다.[1~2] 특히 고출력 전력증폭기의 경우 진행파관을 이용한 진행파관증폭기 (TWTA, Travelling Wave Tube Amplifier)에서 MMIC 소자를 사용한 고체전자소자 형태의 전력증폭기로 서서히 대치되고 있다. 고체전자소자 기술을 사용한 전력증폭기는 TWTA에 비해 소형화, 경량화, 낮은 동작전압, 긴 수명, 유지보수의 용이성 등 여러 장점을 가지고 있다.

그러나, 주파수가 높아질수록 단일의 MMIC만으로 는 높은 출력전력을 가지는 전력증폭기를 구현하기 어

Chungnam National University)

접수일자: 2009년11월12일, 수정완료일: 2009년12월14일

<sup>\*</sup> 학생회원, \*\* 평생회원, 충남대학교 전파공학과 (Dept. of Radio Science and Engineering,

<sup>※</sup> 본 연구는 한국과학기술원 전파탐지특화연구센터를 통한 국방과학연구소의 연구비 지원으로 수행되었 스니다.

려우므로 밀리미터파 영역과 같은 높은 주파수 영역에서는 높은 출력전력을 얻기 위해 다수의 MMIC를 연결하여 출력전력을 높이는 방법을 사용한다. [5~6] 밀리미터파 영역에서 여러 단의 MMIC를 한꺼번에 사용하여 설계할 경우 설계에서 발생하는 설계오류를 파악하기 힘들며 개별부품들이 오동작시 전체 모듈이 오동작하기 때문에 개별부품의 대치를 통한 수리가 어렵게된다. 이러한 문제를 해결하고 각 단의 MMIC 성능 측정을 가능하게 하기 위하여 캐리어를 이용한 MIC (Microwave Integrated Circuit) 복합모듈 설계 방법을사용할 수 있다.

본 논문에서는 캐리어를 이용한 MIC 복합모듈 설계 방법을 사용하여 밀리미터파 영역, 즉 Ka-대역 중심주 파수 영역에서 동작하는 10 W 전력증폭기 모듈을 설계 하고 제작하였다. 또한 전력증폭기 모듈 측정결과에서 나타난 펄스신호의 상승시간에 의한 출력전력의 감소 문제를 해결하기 위해 TTL(Transistor Transistor Logic)을 이용한 펄스 타이밍 제어 기법을 새로이 적용 하였다. TTL 펄스 타이밍 기법은 구동증폭단과 전력증 폭단의 동작 타이밍을 달리함으로써 펄스모드 동작의 효율성을 높이는 기법이다. Ka-대역 전력증폭기의 경 우 국내외적으로 1 W급의 전력증폭기만이 상용으로 가 용한 상태이며, 10 W 전력증폭기의 경우 군수통제에 의해 기술 자료의 확보가 어려우며 국내개발 또한 최근 에서야 이루어졌다.<sup>[7]</sup> 본 논문의 Ⅱ장에서는 Ka-대역 10 W 전력증폭기 모듈의 설계 및 제작에 대한 내용들 을 다루며, Ⅲ장에서는 전력증폭기의 전력감소 문제를 개선하는 TTL 펄스 타이밍 회로를 제시하며 IV장에서 는 10 W 전력증폭기의 측정결과를 제시하고자 한다.

### Ⅱ. Ka-대역 10 W 전력증폭기 모듈의 설계 및 제작

#### 1. 개별블록 구성

본 논문에서 구현하고자 하는 전력증폭기 모듈의 설계목표는 Ka-대역의 중심주파수를 기준으로 2 %의 대역폭을 가지며 65 dB의 선형전력이득과 10 W의 출력전력을 달성하는 것이다. 증폭기의 이득은 65 dB로 설정되었으나 증폭기의 앞 단에 위치하는 PLL(Phase Locked Loop) 주파수합성기의 출력이 충분히 여유가 있어 증폭모듈의 이득이 다소 떨어져도 전체 시스템의동작에는 아무런 문제가 되지 않는다. 따라서 설계, 제

#### 표 1. 전력모듈에 사용된 MMIC 특성 (데이터시트 기준)

Table 1. MMIC characteristics. (based on data sheet)

|          | MMIC     | 출력<br>전력         | 이득    | 동작전압                          |

|----------|----------|------------------|-------|-------------------------------|

| Fujitsu  | FMM5704X | 9 dBm<br>(P1dB)  | 18 dB | 3 V, 20 mA (self bias)        |

| Triquint | TGA4522  | 27 dBm<br>(P1dB) | 18 dB | 6 V, 400 mA<br>(Vg = -0.6 V)  |

| Triquint | TGA4516  | 33 dBm<br>(Psat) | 18 dB | 6 V, 1050 mA<br>(Vg = -0.6 V) |

| Triquint | TGA4517  | 35 dBm<br>(Psat) | 15 dB | 6 V, 2 A<br>(Vg = -0.5 V)     |

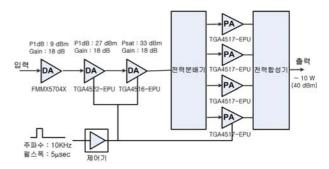

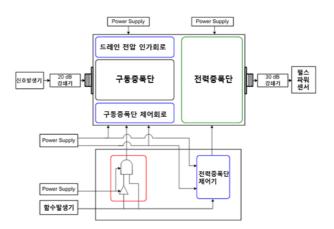

그림 1. 전력증폭기 모듈 구성도

Fig. 1. A block diagram of the power amplifier module.

작의 주된 목표는 10 W의 출력을 대역폭 내에서 얻는 것이다. 10 W 전력모듈의 개발을 위해 별도로 제작된 MMIC 칩들을 사용하는 것이 아니라 상용으로 가용한 칩들을 활용하는 것이기 때문에 칩 선정에 있어 이러한 점들을 충분히 고려하였다. 여기서는 설계목표를 충족하는 전력증폭기 모듈을 위해 Fujitsu사와 Triquint사의 MMIC 칩을 선정하였고 그 특성들을 데이터시트 기준으로 표 1에 정리하였다.

그림 1은 선정한 MMIC 칩을 사용하여 구성한 10 W 전력증폭기 모듈의 블록도를 보여주고 있다. 앞의 3단 증폭기를 사용하여 이득을 충분히 확보한 뒤 전력분배기를 통해 전력증폭단의 4개의 MMIC에 전력을 공급한다. 전력증폭단의 4개의 MMIC에서 증폭된 전력은 전력합성기를 통해 합성함으로써 10 W의 출력전력을 구현하고자 했다. 또한 전력증폭기 모듈을 펄스모드로 동작시키기 위해 각 MMIC의 게이트 전압을 제어할 수있는 게이트 전압 제어기를 설계하고 적용하였다. 전력증폭기 모듈은 조립 및 개별측정, 수리의 용이성을 위하여 기능별로 각각 Silvar로 구성된 캐리어 위에 MIC 실장기술을 사용하여 칩을 조립하였다. 마이크로스트립

으로 구성된 캐리어 모듈들을 본당 와이어로 직접 연결할 경우, 캐리어의 깊이와 간격에 따라 주파수가 높아질수록 임피던스 부정합에 의해 삽입손실이 커지게 된다. 반면에 CPW(Coplanar Waveguide)의 경우 전자계가 윗면에 주로 형성되어 있어 이를 활용하여 연결할경우 캐리어 깊이의 영향을 적게 받아 낮은 삽입손실을가질 수 있다. 따라서 캐리어로 구성된 단위모듈들을이용하여 MIC 복합모듈을 구성할 때 밀리미터파 대역에서 삽입손실 및 반사손실 특성이 우수한 새로운 형태의 CBFGCPW(Conductor Backed Finite Ground CPW)-Microstrip 천이구조를 사용하여 설계하였다. [8]

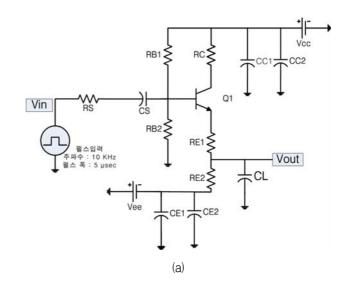

#### 2. 펄스 전압 제어기

전력증폭기 모듈을 펄스모드로 동작시키는 방법에는 입력신호를 펄스로 변조하여 증폭기에 직접 입력하는 방법과 증폭기 전원전압을 on/off 시키는 방법이 있 다.[9] 본 논문에서는 전력증폭기 모듈의 펄스 구동 방 법으로 증폭기 전원전압을 on/off 시키는 방법 중 게이 트 전압을 펄스로 제어하는 방법을 사용하였다. 회로의 게이트를 펄스로 제어하는 방법은 드레인을 제어하는 방법보다 적은 전류로 동작할 수 있어 제어기 회로가 간단해질 수 있으며 큰 전류를 직접 공급하고 차단할 때보다 회로의 동작속도가 빠르다. 게이트 전압 제어기 에미터팔로워(emitter 트랜지스터를 이용한 follower) 회로를 사용하였다. 트랜지스터는 NEC사의 2SC4226을 사용하였고 설계는 Agilent사의 ADS 소프 트웨어를 사용하였다. 그림 2는 설계된 제어기 회로를 보여주고 있다.

제어기에서 나오는 출력은 각 MMIC의 게이트 단자로 연결되며 MMIC 게이트 단자에 존재하는 바이패스 (bypass) 캐패시터와 바이어스 연결을 위한 피드스루 (feed thru)에 존재하는 캐패시터는 게이트 전압 제어기의 부하로 작용하게 된다. 따라서 게이트 전압 제어기설계에서 두 캐패시터 값을 부하 캐패시터로 고려하여제어기를 설계하였다. 설계 결과 MMIC를 on 시킬 수있는 -0.6 V에서 off 시킬 수 있는 -1.3 V의 전압을 보이는 펄스 파형을 구현하였으며 펄스 상승시간이 약800 nsec 임을 확인하였다.

#### 3. Ka-대역 10 W 전력증폭기 모듈 제작

그림 3은 제작된 10 W 전력증폭기 모듈을 보여주고 있다. 전력증폭기 모듈은 크게 구동증폭단과 전력증폭

그림 2. 게이트 펄스 전압 제어기 회로 (CL = 23 nF) (a) 회로도 (b) ADS 시뮬레이션 결과

Fig. 2. A gate pulse voltage control circuit (CL = 23 nF).

(a) a schematic circuit (b) simulation results

단으로 나눌 수 있다. 그림에서 A 부분은 구동증폭단의 드레인 바이어스를 인가하기 위한 회로이고, B 부분은 구동증폭단 및 전력증폭단 MMIC의 게이트 전압을 제어하기 위한 게이트 전압 제어기이다. C 부분은 구동증폭단 모듈을 나타내며, D 부분은 전력을 분배 및 합성하기 위한 4-출력 전력분배기와 전력증폭을 위해 MMIC 4개가 병렬로 연결된 모습을 나타낸다. 전력증폭기 모듈의 크기는 72 mm × 62 mm이다.

#### Ⅲ. TTL을 이용한 펄스 타이밍 제어

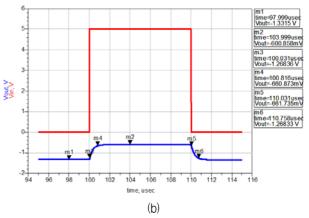

#### 1. 부하 캐패시터와 펄스 상승시간

앞에서 언급한 것처럼 각 MMIC 게이트 단자에 존재하는 바이패스 캐패시터와 바이어스 연결을 위한 피드

그림 3. 제작된 10 W 전력증폭기 모듈

Fig. 3. A fabricated 10 W power amplifier module.

그림 4. 부하 캐패시터에 따른 상승시간 측정결과 Fig. 4. Measured results of the rise time with the load capacitance values.

스루 캐패시터는 게이트 전압 제어기의 부하로 작용하 게 된다. 부하로 작용하는 캐패시터 값에 따라 펄스의 상승시간이 영향을 받게 되며 부하 캐패시터에 따른 상 승시간의 변화를 그림 4에 나타내었다. 바이패스 캐패 시터 및 피드스루 캐패시터의 값을 모두 고려하면 약 23 nF 이다. 따라서 측정된 그래프의 값을 비교해 보면 상승시간이 약 700 nsec임을 알 수 있다. 시뮬레이션 결과와 측정결과가 약간의 차이를 보이는 것은 다수의 SLC(Single Layer Capacitor)를 연결하는 과정에서 사 용된 와이어본딩 효과 때문이다.

#### 2. TTL을 이용한 펄스 타이밍 제어

게이트에 전원전압 펄스를 똑같은 시점에 인가할 경우 구동증폭단과 전력증폭단은 게이트 입력 캐피시턴스의 차이로 인해 다른 시점에서 동작하게 된다. 즉, 상대적으 로 큰 부하 캐패시턴스를 가지는 전력증폭단이 구동증폭

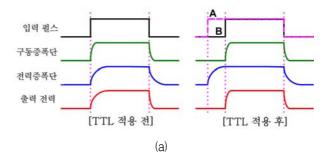

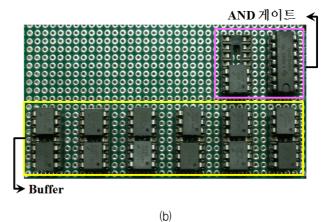

그림 5. 펄스 타이밍 제어회로 (a) 펄스 신호 비교 (b) 펄스 타이밍 제어회로

Fig. 5. Pulse timing control circuit (a) pulse signal comparison (b) pulse timing control circuit.

단보다 늦게 on 되어 전체회로의 on 시점을 지연시키게된다. 반면에 회로가 off 되는 시점은 구동증폭단이 전력증폭단보다 빨리 off 되므로 구동증폭단이 결정하게된다. 따라서 회로의 동작시간은 전력증폭단이 on 되는 시점과 구동증폭단이 off 되는 시점으로 결정나게된다. 전력증폭단에 의한 전체회로의 동작 지연은 동일한 펄스구동조건에서 동작지연이 없는 회로보다 작은 출력전력을 가지게된다. 전력증폭단의 펄스 상승시간 지연에의한 출력전력의 감소 문제를 개선하기위해 구동증폭단과전력증폭단의 입력 펄스를 다른 시점에 인가하는 펄스타이밍 제어회로를 TTL 소자를 활용하여구현하였다.

그림 5(a)에서는 전력증폭단과 구동증폭단에 인가되는 필스 파형에 대해 필스 타이밍 회로를 사용하기 전과 후를 비교하여 나타내었다. 필스 타이밍 제어를 적용하기 전에는 구동증폭단과 전력증폭단에 필스의 폭을 똑같이 인가하였지만, 필스 타이밍 제어를 적용하면 전력증폭단의 필스폭(A)이 더 길게 된 상태에서 구동증폭단의 필스(B)보다 먼저 인가된다. 그림 5(b)에서는 TTL을 이용하여 구현한 제어회로를 나타내고 있다.[10] 다단 버피회로는 함수발생기에서 나오는 필스 신호를

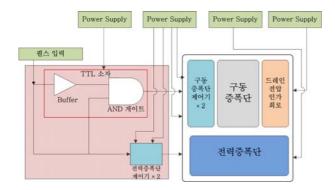

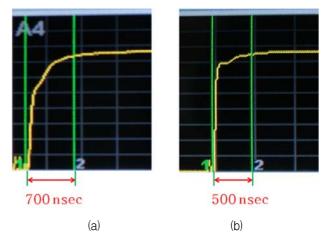

그림 6. 펄스 타이밍 제어를 적용한 전력증폭기 블럭도 Fig. 6. Power amplifier block diagram with pulse timing control circuits.

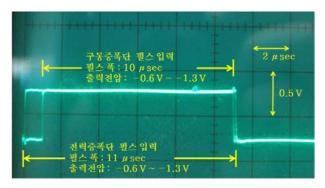

그림 7. 펄스 타이밍 제어회로 측정 결과 Fig. 7. Measured results of the pulse timing of

Fig. 7. Measured results of the pulse timing control circuit.

지연시키는 역할을 하고, AND 게이트를 이용하여 지연된 펄스 신호와 함수발생기에서 나오는 펄스 신호를 곱하게 된다. 다단 버퍼에 의해 지연된 펄스 신호는 구동증폭단에 인가되며 전력증폭단보다 짧은 펄스 신호가된다. 이와 같이 회로를 구성한 이유는 구동증폭단과 전력증폭단의 펄스 신호가 동시에 off 되도록 설정하기위함이다.

그림 6는 본 논문에서 제안하는 펄스 타이밍 제어 기법을 적용한 전력증폭기 블록도를 보여주고 있다. 블록도에 나타난 것처럼 게이트를 제어하는 입력 펄스 신호는 버퍼와 AND 게이트를 통해 구동증폭단으로 이어지는 경로와 직접 전력증폭단의 게이트 펄스 제어회로로이어지는 경로로 나누어진다. 두 경로를 통해 전달되는게이트 제어 펄스는 그림 7과 같이 측정되었다.

그림 7에서는 펄스 타이밍 제어회로를 통하여 전력 증폭 모듈의 게이트 입력단자에 인가되는 펄스를 측정한 결과이다. 측정결과에서처럼 구동증폭단의 펄스는 전력증폭단의 펄스보다 약 1 µsec 지연되어 출력되고 있으며 펄스폭도 1 µsec 정도 작다는 것을 보여주고 있

다. 설계된 펄스 타이밍 제어회로의 출력전압은 전력증 폭기가 필요로 하는 게이트 제어 전압인  $-0.6 \sim -1.3$ V의 값을 가지고 있다.

# IV. TTL 펄스 타이밍 제어 회로를 적용한 Ka-대역 10 W 전력증폭기 모듈 측정

이 장에서는 TTL 펄스 타이밍 제어회로가 적용된 경우와 그렇지 않은 경우에 대한 Ka-대역 10 W 전력 증폭기 측정결과를 비교한다. 그림 8은 10 W Ka-대역 전력증폭기 모듈을 측정하기 위한 장비 구성을 나타낸 다. 게이트 전압 제어기에 바이어스와 펄스를 인가하기 위한 전원공급기 및 함수발생기, 구동증폭단에 드레인 바이어스 전원을 공급하기 위한 전원공급기, 전력증폭 단에 드레인 바이어스 전원을 공급하기 위한 고전력 전 원공급기, 전력증폭기 모듈에 RF 신호를 인가하기 위한 신호발생기, 전력증폭기 모듈의 출력전력을 측정하기 위한 파워미터 및 파워센서를 사용하였다. 그리고 측정 에서 발생하는 열을 원활히 제거하기 위해 알루미늄 재 질의 방열판을 이용하였다. 전력증폭기 모듈에 인가되 는 RF 신호의 크기를 줄이기 위해 전력증폭기의 입력 쪽에 20 dB 감쇄기를 사용하였으며, 증폭된 출력신호가 파워미터 및 파워센서의 측정 범위를 넘어서지 않도록 전력증폭기의 출력 쪽에 30 dB 감쇄기를 사용하였다. 전력증폭단에 전원을 공급하는 전원공급기의 전류 공급 능력이 게이트 전압 제어기의 스위칭 속도를 따라갈 수 없기 때문에 전력증폭단의 드레인 바이어스 부분에 대 용량의 캐패시터를 사용하여 순간적인 전류 공급이 가

그림 8. 제작된 전력증폭기 모듈의 측정 장비 구성 Fig. 8. Power measurement setup for the fabricated power amplifier module.

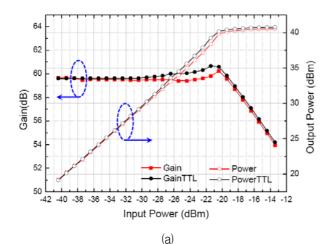

그림 9. TTL 펄스 타이밍 제어회로가 적용되기 전과 후의 10 W 전력증폭기 모듈의 펄스모드 전력 측정 (a) 입력전력에 대한 출력전력과 이득 (b) 주파수에 따른 포화전력 변화

Fig. 9. Pulsed power measurement of 10 W power amplifier modules with/without TTL pulse timing control circuits (a) output power and power gain with input power (b) frequency dependence of the saturated output power.

#### 능하도록 하였다.

그림 9에서는 Ka-대역 10 W 전력증폭기에 필스 타이밍 제어회로를 적용하기 전과 적용한 후의 출력전력을 중심주파수 영역에서 드레인 전압이 6.5 V일 때 측정한 결과이다. 전력증폭기 모듈의 측정을 위해 게이트전압 제어기에 주파수 10 kHz, 5 µsec의 필스폭을 갖는 구형파를 인가한 후 측정하였다. 측정한 결과 전력이득은 약 59.5 dB이고, 출력전력은 필스 타이밍 제어회로를 적용한 전력증폭기 모듈이 11.89 W(40.75 dBm)였으며 필스 타이밍 제어회로를 적용하지 않은 전력증폭기

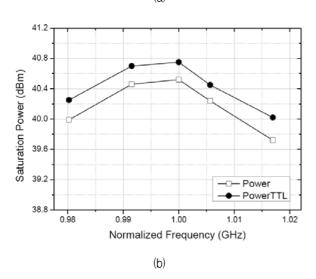

그림 10. TTL 펄스 타이밍 제어회로를 적용하기 전과 후 의 출력파형 상승시간 비교 (a) 적용 전 (b) 적용 후

Fig. 10. Rise time comparison of the output waveforms

(a) without TTL timing control circuits (b) with TTL timing control circuits.

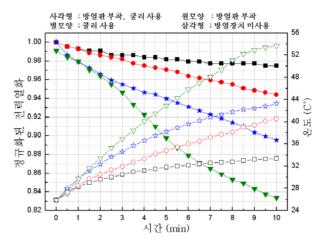

그림 11. 전력증폭기 모듈의 운용시간에 따른 정규화한 출력전력의 열화

Fig. 11. Normalized output power degradation with the power amplifier operation time.

모듈은 11.27 W(40.52 dBm)였다. 펄스 타이밍 제어회로만으로 약 0.62 W의 전력이 향상되었음 확인하였다. 그림 9(b)에 나타난 바와 같이 정규화한 중심주파수(f<sub>o</sub>)를 기준으로 0.98f<sub>o</sub> ~ 1.02f<sub>o</sub>의 주파수 범위에서 전체적으로 출력전력의 특성이 고르게 향상되었으며 전체 주파수 영역에서 10 W 이상의 출력전력이 확보되었다.

그림 10에서는 파워미터에서 측정된 펄스 출력전력 파형에 나타난 상승시간의 모습을 보여주고 있다. TTL 펄스 타이밍 제어 기법을 적용함으로써 펄스 출력전력의 상승시간이 200 nsec 가량 개선되었다. 파워미터의 출력파형을 보면 상승시간이 200 nsec가 줄어들었지만

핀치오프(pinch-off) 전압을 고려한 MMIC 회로의 on/off로 계산하면 펄스 타이밍 제어를 적용한 파형이 훨씬 빠르게 on이 되는 것을 알 수 있다.

그림 11은 Ka-대역 10 W 전력증폭기 모듈의 운용시간에 따른 출력전력의 전력열화 특성을 측정값을 기준으로 정규화하여 나타내었다. 전력증폭기 모듈에 방열판 등을 활용하여 방열대책을 세운 경우 10분의 운용시간에 대해 전력의 열화 특성이 약 3 % 이내로 유지되었고 방열판을 사용하지 않고 운용한 경우 16 %정도의 열화 특성이 측정되었다. 그러나 고정밀 유도탄등에 사용되는 전력증폭기 모듈처럼 운용시간이 1~2분이내로 짧은 경우 방열판만을 사용하더라도 출력전력의 성능 변동사항은 발생하지 않아 개발된 전력증폭기 모듈이 신뢰성 있게 실제로 운용될 수 있음을 확인하였다.

#### Ⅴ. 결 론

본 논문에서는 그동안 국내개발이 이루어지고 있지 않았던 Ka-대역 10 W 전력증폭기 모듈을 캐리어를 이용한 MIC 복합모듈 설계 방법을 사용하여 제작하였 다. 각 증폭기 MMIC를 기능별 캐리어를 사용하여 특 성을 파악하였으며 제작한 전력증폭기의 펄스동작을 위한 게이트 전압제어기를 설계, 제작하였다. 제작한 전력증폭기 모듈은 중심주파수에서 11.27 W의 출력전 력을 나타내었다. 펄스모드 전력증폭기 모듈의 부하 캐 패시턴스에 의한 펄스 상승시간 증가와 이에 따른 전 력감소 특성을 개선하기 위해 새로운 TTL 펄스 타이 밍 기법을 적용하였다. 펄스 타이밍 기법은 전력증폭기 모듈의 출력전력을 중심주파수에서 0.62 W 정도 향상 시켜 출력전력을 11.89 W로 증가시켰다. 제작한 전력 증폭기 모듈은 밀리미터파 대역의 레이더 시스템뿐만 아니라 향후 활성화될 것으로 기대되는 밀리미터파 대 역의 민간통신용 고출력 시스템에도 유용하게 활용될 수 있을 것이다.

#### 참 고 문 헌

- [1] M. S. Uhm, D. P. Jang, I. B Yom, and S. P. Lee, "A Gain-Variable Ka-band SSPA using MMIC Technology," *Asia-Pacific Microwave Conference*, pp. 617–620, Sydney, Australia, Dec. 2000

- [2] M/A-COM Inc., "High Voltage, Low Cost FETs for HPA MMIC Applications," *Microwave Journal*, vol. 47, no. 12, pp. 126, Dec. 2004

- [3] A. R. Barnes, M. T. Moore, M. B. Allenson, and R. G. Davis, "A Compact 6 to 18 GHz Power Amplifier Module with 10W Output Power", IEEE MTT-S International Microwave Symposium Digest, vol. 3, pp. 959–962, Anaheim, USA, June 1999

- [4] 조창환, 이찬주, 홍의석, "Ku-band의 소형 기지국 용을 위한 8 W 고출력 증폭기에 관한 연구", 한국 전자파학회논문지, 7권 1호, pp. 53-60, 1996년 3월

- [5] T. Murae., K. Fujii, and T. Matsuno, "A Compact S-band MMIC High Power Amplifier Module", IEEE MTT-S International Microwave Symposium Digest, vol. 2, pp. 943-946, Boston, USA, June 2000

- [6] M. Funada, K. Seino, K. Takita, Y. Itoh, G. Toyoshima, T. Takagi, M. Komaru, H. Mizutamari, H. Mineno, C. Ohuchi, T. Nishigaki, M. Takouchi, M. Nishida and H. Saito, "Ka-band 20 W-class SSPA utilizing MMIC Technology for Satellite Communications", 25th European Microwave Conference, vol. 1, pp. 12–15, Bologna, Italy, Oct. 1995

- [7] 김경학, 박미라, 김동욱, "Ka-대역 10 W 전력증폭기 모듈의 설계 및 제작", 한국전자파학회논문지, 20권 3호, pp. 264-272, 2009년 3월

- [8] 임주현, 양승식, 염경환, "저손실을 갖는 CBFGCPW- Microstrip 천이구조의 해석 및 MIC 모듈 집적화에 응용", 한국전자파학회논문지, 18권 7호, pp. 809-818, 2007년 7월

- [9] 이희민, 홍성용, "Pulsed Power Amplifier를 위한 고속 스위칭 회로 설계", 한국전자파학회논문지, 19권 2호, pp. 174-180, 2008년 2월

- [10] http://www.fairchildsemi.com

#### - 저 자 소 개 -

장 석 현(학생회원)

2009년 충남대학교 전기정보통신 공학부 학사 졸업.

2009년~현재 충남대학교 전파공학과 석사과정.

<주관심분야: RF 회로 및 레이 더 모듈 설계>

김 경 학(학생회원)

2007년 충남대학교 전기정보통신 공학부 학사 졸업.

2007년~현재 충남대학교 전파공학과 석사과정.

<주관심분야: 초고주파 능동회로 설계, 전력증폭기 모둘 설계>

권 태 민(학생회원)

2009년 충남대학교 전기정보통신 공학부 학사 졸업.

2009년~현재 충남대학교 전파공학과 석사과정.

<주관심분야: 반도체 회로 설계, 레이더 모듈 설계>

김 동 욱(평생회원)

1990년 한양대학교 전자통신 공학과 학사 졸업.

1992년 한국과학기술원 전기및 전자공학과 석사 졸업.

1996년 한국과학기술원 전기및 전자공학과 박사 졸업.

1991년~2000년 LG종합기술원 선임연구원 2000년~2002년 (주)텔레포스 연구소장 2002년~2004년 에스원 기술연구소 응용기술팀장 2004년~현재 충남대학교 전파공학과 교수 <주관심분야: 초고속 및 초고주파 집적회로, 초 소형 레이더 모듈, 밀리미터파 전력증폭기 모듈>